1 ML2724简介 ML2724是Micro Linear公司的一款高性能的广泛应用于2.4GHz快速跳频通信系统的单片集成收发芯片,它集成了本振、抗镜像Ⅳ滤波器和基带低通滤波器、限幅器、数据判决器,并且自带了一个可编程控制的频率合成器,具有同步指示和与基带处理相接的各种端口。它具有以下主要特点: (1)能够完成2.4GHz通信系统的收发功能的集成单芯片; (2)信道间隔为2.048MHz,具有80个信道; (3)完全集成了所有的Ⅲ滤波器和数据滤波器; (4)灵敏度为-90dBm; (5)内部集成了完整的1.6GHz的频率合成器; (6)作为FHSS发射,能够达到1600跳/秒; (7)可以利用一个3线的接口可编程控制PLL; (8)具有模拟接收信号强度指示(RSSl); (9)在2.4GHz时,传输距离10m~1000m,传输速度可达1.5Mbps; (10)可以应用于TDD和TDMA通信系统中。 其内部原理框图如图1所示。

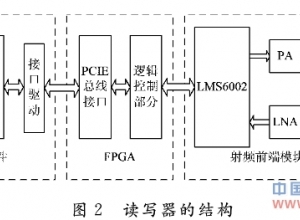

2 系统的组成原理与设计 2.1系统的组成原理 笔者设计的2.4GHz快速跳频系统的组成原理如图2所示。系统主要由ML2724和DSP完成,该系统能达到1600跳/秒。如果跳频图案为正交排列,本系统的跳频点数最大可以为80个,非正交排列则为40个,在跳频带宽范围内,跳频间隔为1.024MHz,中心频率为2.4GHz,跳频处理增益分别为16dB(正交)、16dB(非正交);DSP完成基带信号的编解码处理、跳频同.步控制、收发控制,以及跳频同步信息的提取和语音编解码器的控制。语音编码可以采用AMBE2000实现,也可以采用MC3518实现CVSD的语音编码。下面将探讨跳频信道的分配、跳频图案的设计,以及跳频同步问题。 2.2 跳频信道的设置 如果按ML2724内部的分频点规则,邻近频率间隔不重叠(非正交排列),系统的跳频点数最多只能有40个频点,由于跳频点数太少不能满足系统抗干扰指标,所以本系统中采用了相邻频点间正交排列方式,如图3所示。即允许发射频率的间隔重叠,间隔为1.024MHz,虽然正交排列与常规排列方式的系统带宽相同,但是跳频点数增加了一倍,跳频处理增益获得3dB的提高。 2.3 跳频图案和序列的设计 由于受系统工作频点的限制,频点只能在80个(正交排列)的频点中伪随机地选取。从跳频系统性能上讲,系统对跳频图案的产生和性能有如下要求: (1)跳频图案的周期性应足够长,线性复杂度应足够大,以达到高保密度的性能和强的抗破译性; (2)同一网内各用户间的跳频图案的互相关性能要好,跳频图案的自相关性能也要良好,以减小因碰撞带来的信噪比损失; (3)具有较好的随机性,使其不易被他方捕获和解密; (4)各频点在频带内均匀分布,以增强抗干扰性能; (5)跳频指令码的数量要多,可更换,以便多网使用,这样可进一步提高系统的抗截获性。

从国内外资料和研究来看,跳频图案的构造通常采用m序列、M序列、Gold码和钟控码等产生。这些码各有优缺点,其中钟控码性能最好且数量多;非线性码相关性能较好、编码复杂度高、难于破译,但结构复杂,挑选码比较困难;Gold码数量多,周期长,具有三值互相关性;RS码相关性好,但周期短;M序列也属于非线形码,其数量虽多,但相关性差;m序列相关性能好,实现简单,但数量少。综合各方面的因素,笔者采用了理论研究最完备、易于产生的m序列,并通过非线性变换的方法,增加序列的复杂度,并使其非线性化、具有优良的自相关和互相关性能。A.Lempl和H.Greenberger于1974年提出了具有最佳汉明相关性能的跳频序列簇的构造模型,它是基于有限域GF(P)上的n级m序列发生器。以发生器的众个相邻级(k≤n)与某个k项逐项模P相加后,去控制频率合成器,此模型称为L-G模型。L-G模型中存在严重的频点滞留问题:每当在移位寄存器中出现n重XX…X,XεGF(P),X≠0,输入到频率合成器的是连续n-k+1跳变的k重XX…X。这样信号在某个频率上停留相当长的时间,很容易被非法接收机检测。 因此,在L-G模型上进行改进,采用了k个非相邻级缓解频点滞留问题,采用平滑替代算法[5]进行跳频图案的宽间隔处理。定义频带F: F={f1|0≤i≤N-1} 只要满足|fi+1-fi|≥d就称为宽间隔跳频点,反之称为窄点。对于窄点有修正关系式: PN(i+1)=[PN(i)+d]modN 其中,N为跳频频点数;d为跳频间隔;PN(i)为跳频码号。 这样对窄点通过修正处理后,在频域F上所确定的频率点就构成了所需要的宽间隔跳频图案集。这种方法不需要构造对偶频点或者对偶频带,保证了伪码序列的随机性,又等于进行了第二次非线性变换,使伪码(m序列)的非线性化程度和抗破译能力大大增强。从而得到既满足宽间隔要求,又克服L-G模型缺点的宽间隔跳频图案,构造模型如图4所示。这种跳频序列构造模型用FPGA或CPLD实现是不难的,但从系统成本出发,利用带ARM内核的DSP实现。而跳频频率合成器当然就利用ML2724内部所集成的频率合成器。

2.4 系统的同步问题考虑 跳频系统的同步是成功通信的前提条件。如果没有同步,也就无法解调出信码,跳频系统的抗干扰也就无法发挥。由于收发时钟的不一致性、跳频序列的启动时差、电波传播时延等因素,接收端启动的跳频序列与接收到的发送跳频序列开始总是不同步的。因此,收端必须采用一定的技术措施迫使本地跳频序列与发端的跳频序列同步,这就是跳频码的捕获;在取得同步之后,噪声及一些外来因素的干扰还会迫使已取得的同步出现失锁现象,为此还应采取保持同步的技术,这就是同步跟踪。 跳频同步是系统初始同步、迟入网勤务同步和快速同步三者的有机结合。初始同步是网内用户通过搜索初始同步信息而快速达到同步进入正常通信,

是通信双方沟通的主要手段;勤务同步是迟于初始同步信息发送之后而处于搜索状态的用户,通过搜索网内用户数据流中插入的同步信息来及时加入网内通信,同时勤务信息也是同步保持及快速同步的保证。同步的建立离不开同步信息。本系统设计的同步信息内容包括相关码、标记、位同步、网号、频率表示号、TOD及其他信息。通信开始时,接收机不断地搜索同步信息,当从四个循环频率中检测到两次同步信息,则认为抓到了同步,并根据相关码和标志,确定出通信的起始时刻;并后续地跳频点传送相同的位同步、网号、频率号信息。为了增加抗干扰能力,采用择多判决。最后,接收完TOD信息后,即可换算出对应的跳频图案,开始数据或数字话音信息的传输。

为了使电台有迟后入网和同步保持的功能,需在传输数据流中携带一定的同步信息(勤务同步),以满足通信的要求。迟入网同步中,如在此帧检测失败,则下帧继续搜索,直到抓住正确的勤务同步信息为止。另外,利用每帧中的勤务同步信息可实现同步保持。在每帧同步信息出现时,接收机在出现相关码、标记的跳频区域加大搜索窗口,利用收到的相关信息,调整发生偏移的跳频时钟,达到同步保持的目的。

是通信双方沟通的主要手段;勤务同步是迟于初始同步信息发送之后而处于搜索状态的用户,通过搜索网内用户数据流中插入的同步信息来及时加入网内通信,同时勤务信息也是同步保持及快速同步的保证。同步的建立离不开同步信息。本系统设计的同步信息内容包括相关码、标记、位同步、网号、频率表示号、TOD及其他信息。通信开始时,接收机不断地搜索同步信息,当从四个循环频率中检测到两次同步信息,则认为抓到了同步,并根据相关码和标志,确定出通信的起始时刻;并后续地跳频点传送相同的位同步、网号、频率号信息。为了增加抗干扰能力,采用择多判决。最后,接收完TOD信息后,即可换算出对应的跳频图案,开始数据或数字话音信息的传输。

为了使电台有迟后入网和同步保持的功能,需在传输数据流中携带一定的同步信息(勤务同步),以满足通信的要求。迟入网同步中,如在此帧检测失败,则下帧继续搜索,直到抓住正确的勤务同步信息为止。另外,利用每帧中的勤务同步信息可实现同步保持。在每帧同步信息出现时,接收机在出现相关码、标记的跳频区域加大搜索窗口,利用收到的相关信息,调整发生偏移的跳频时钟,达到同步保持的目的。3 系统的软件设计 系统同步的软件设计主要考虑接收部分的初始同步捕获和同步处理。接收同步处理由DSP协同ML2724共同完成,DSP(带ARM内核)从ML2724提取同步信息,经过相关运算,判断跳频是否达到同步。获得初同步以后,数据交由DSP完成主要的同步处理过程。系统接收同步过程的软件流程如图5所示。 在通信技术领域,扩、跳频技术以其低截获率、保密性好、抗干扰、抗衰落能力强、多址连接灵活、对窄带信号干扰小等特点,显示出其他传输体制无与伦比的优越性,广泛应用于雷达、导航、通信、遥控遥测等各个领域,尤其是在军事通信方面的成功应用,受到了各国军方的高度重视。在民用方面,跳频技术也有广泛的应用,在频率资源日益紧张的现代无线通信中,跳频通信系统通过跳频调制伪码的优良的自、互相关特性,实现多址,增大系统容量。本文所设计的2.4GHz快速跳频系统可以广泛应用在小局域无线通信系统,例如目前比较热门的无线局域网中,尤其可以采用无线局域网的组网方式,实现热点地区的无线覆盖。(综合电子论坛)

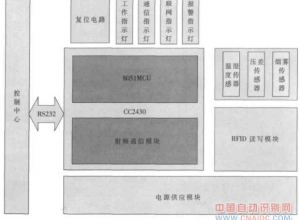

![基于二进制防碰撞算法的RFID定位系统的设计[图]](http://www.cnaidc.com/file/upload/201312/26/16-40-04-98-1.gif)